非易失存储中的新星:忆阻器---姚卫博士

2021-01-13

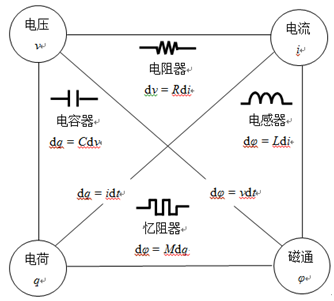

1971年,蔡少棠(L.O. Chua)教授在论文“Memristor-The missing circuit element”中首次提出忆阻器(Memristor)这个概念[1]。蔡教授在研究电压、电流、电荷与磁通量之间的关系时发现,电阻、电容与电感都可以由电压、电流、电荷与磁通量之间的关系表示,如图1.1所示。具体来说,电阻可以用电压与电流之间的关系表示,电容可以用电荷与电压之间的关系表示,电感则可以用电流与磁通量之间的关系表示。然而表示电荷和磁通量之间关系的元件还未曾有人提出,蔡教授称其为忆阻器,其表达式为dφ=Mdq。

图1.1 四种基本元件的关系

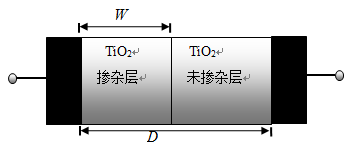

2008年,惠普(HP)公司的科研团队利用TiO2成功制造出了第一个忆阻器实物[2]。图1.2表示HP忆阻器的原理图,其中D表示以TiO2为主体的宽度,W是掺杂氧空位层的宽度。忆阻器的两端在电压的激励下,其阻值会随着电流的改变而改变。

图1.2 HP忆阻器

因光刻技术相对滞后,同时缩小晶圆成本倍增等问题,半导体工艺已逼近量子尺寸,导致集成电路设计已进入“后摩尔”时代。当前,动态随机存取存储器(DRAM)以电容器中电荷量的多少来存储数据,数据的保持时间很短。为了保持数据,必须隔一段时间刷新一次,若存储单元未被刷新,存储信息就会丢失。为了增加数据的保留时间,电容器必须设计得足够大以降低刷新频率,而这样会导致容量和能耗受限,工艺难度加大。而且内存容量的增长速度远低于CPU性能的增长速度。另外服务器大约一半的能耗来自内存,DRAM的能耗中有40%来自刷新,因此,随着容量的不断增大,泄漏功耗将进一步增加。来自IDC的数据,2019年全球的数据量已达到41ZB,全球数据量维持着高速增长。日益庞大的数据量对存储包括高性能计算的存储,以及各种网络应用的要求会越来越高。忆阻器是一种发展前景远大的纳米器件,它具有高读写速度、高集成密度、低功耗等优势,因此,将成为存储器领域的一颗新星。

目前忆阻器在存储方面的研究主要表现在以下两方面:

(1)单个忆阻器的读写控制[3];

(2)忆阻阵列结构的设计和读写优化控制[3]。

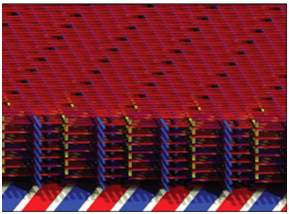

美国闪迪科技公司于2013年使用1D1R结构和MeOx材料设计出32 Gb的忆阻存储芯片[3-4]。次年,美国Micron科技公司使用1TIR结构和CuTe材料制备出了16 Gb的忆阻存储芯片[3, 5]。同时,忆阻存储阵列也可采用三维结构堆放[6-7],如图1.3所示。

图1.3忆阻存储阵列的三维结构

HP忆阻器的物理实现以及忆阻器的应用前景极大地吸引了人们的注意力,各种忆阻器模型及其模拟器相继被设计出来。

目前,忆阻器及其模拟器可以分成以下四类。

(1) 物理模型[8-9]:指通过某些工艺用实际材料制作出具有忆阻特性的物理器件。HP忆阻器是最典型的例子。目前,制造忆阻器物理器件的材料通常为氧化物,如氧化钛,氧化锌等。

(2) 数学模型[10-11]:指根据忆阻的特性构建合适的数学关系式,并能用电路元件实现忆阻器功能的模型。常见的数学模型有分段线性模型、二次非线性模型与三次非线性模型。

(3) Spice模型[12-13]:指利用Spice仿真软件构造的具有忆阻器特性的模型。

(4) 电路模拟型[14-15]:指利用电路元件构造的具有忆阻器特性的模型。因为忆阻器的物理器件还未真正地商用,而数学模型与Spice模型都仅适合理论分析,因此,忆阻器的电路模拟型就显得异常重要。忆阻器的电路模拟型由于是用电路元件构造的具有忆阻器特性的模型,便于应用于相关的硬件电路实验,具有较高的研究价值。

参考文献

[1] Chua L O. Memristor-The missing circuit element. IEEE Transactions on Circuit Theory, 1971, 18(5): 507-519

[2] Strukov D B, Snider G S, Stewart D R, et al. The missing memristor found. Nature, 2008, 453(7191): 80-83

[3] 李清江, 刘海军, 徐晖. 忆阻器的发展现状与未来. 国防科技, 2016, 37(6): 9-16

[4] Liu T Y, Yan T H, Scheuerlein R, et al. A 130.7mm2, 2-Layer 32 Gb ReRAM memory device in 24 nm technology. IEEE Journal of Solid-State Circuits, 2013, 49(1): 140-153

[5] Zahurak J, Miyata K, Fischer M, et al. Process integration of a 27nm, 16Gb Cu ReRAM. IEEE International of Electron Devices Meeting, San Francisco, CA, USA, 2014: IEDM14 (140-143)

[6] Xu X, Luo Q, Gong T, et al. Fully CMOS compatible 3D vertical RRAM with self-aligned self-selective cell enabling sub-5nm scaling., 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 2016.

[7] Chakrabarti B, Lastrasmontaño M A, Adam G, et al. A multiply-add engine with monolithically integrated 3D memristor crossbar/CMOS hybrid circuit. Sci Rep, 2017, 7: 42429

[8] Ju H P, Dong S J, Kim T G. Improved uniformity in the switching characteristics of ZnO-based memristors using Ti sub-oxide layers. Journal of Physics D: Applied Physics, 2017, 50(1): 015104

[9] Sun Z, Wei L, Feng C, et al. Built-in-homojunction-dominated intrinsically rectifying-resistive switching in NiO nanodots for selection-device-free memory application. Advanced Electronic Materials, 2017, 3(1): 1600361

[10] Muthuswamy B. Implementing memristor based chaotic circuits. International Journal of Bifurcation and Chaos, 2010, 20(05): 1002651

[11] Li Q D, Zeng H Z, Li J. Hyperchaos in a 4D memristive circuit with infinitely many stable equilibria. Nonlinear Dynamics, 2015, 79(4): 2295-2308

[12] Yakopcic C, Hasan R, Taha T M, et al. Memristor-based neuron circuit and method for applying learning algorithm in Spice. Electronics Letters, 2014, 50(7): 492-494

[13] Xu K D, Zhang Y H, Yuan M Q, et al. Two memristor Spice models and their applications in microwave devices. IEEE Transactions on Nanotechnology, 2014, 13(3): 607-616

[14] 梁燕, 于东升, 陈昊. 基于模拟电路的新型忆感器等效模型. 物理学报, 2013, 62(15): 15850(1-10)

[15] Kim H, Sah M P, Yang C, et al. Memristor emulator for memristor circuit applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 2012, 59(10): 2422-2431