由通用架构到存内计算架构的深度学习硬件技术-张鑫博士

2022-01-05

扩展现实(XR,包括AR和VR,分别为Augmented Reality和Virtual Reality的缩写)技术的发展,使人们实现现实世界与虚拟世界相互融合与互动的梦想成真。AR/VR是一种由计算机软件开发的模拟环境。它创造了一种看似真实的沉浸体验。由于技术的进步,尤其是在过去五年中VR/AR技术的潜力得到了彻底释放。现在,VR /AR已触及各行各业,成为产业发展的重要技术。

1. VR/AR对人工智能的需求

3D内容(包括3D模型、3D动画,和3D交互等)是VR/AR核心之一。然而,目前各个领域的3D内容尚需要大量人工进行制作,而且对制作人员的门槛要求相对较高,因而产能非常低,这是制约相关行业发展的一大瓶颈。而人工智能(Artificial Intelligence,简称AI)则有望一定程度上实现3D内容制作的自动化,替代部分重复劳动,并提升制作效率。VR和AR的目标都包含了更加自然的交互,这正是AI要解决的目标之一。AlphaGo和AlphaZero证明了AI在一定领域内的智能,而这些领域与VR和AR存在重合,有望弥补VR和AR的智能性。

深度学习(Deep Learning,简称DL)是人工智能中的一个核心子集。近年来,DL[1]在图像分类、理解语音、玩视频游戏和语言之间翻译等任务上的改进越来越接近人类的技能水平。由于需要大量的训练数据和参数,现代深度神经网络(Deep Neural Network,简称DNN)需要付出高昂的训练成本,限制了大量应用,如VR/AR等,对DNN智能解决方案的需求。DL对算力的要求越来越高,催生底层硬件技术的发展。

下面我们试图阐述深度学习对硬件的依赖,不同硬件支持下的深度学习是如何工作的,以及DL的内存计算(In-Memory Computing,简称IMC),指出了高性能、低功耗DL硬件的发展方向。

2. 深度学习对硬件的依赖

DL模型就像一个拥有数百万(甚至更多)可调参数的巨大自组织的试错机器。在给机器输入大数据并进行数千万或数亿次训练周期的迭代后,机器可以找到与 DL 模型相关的最佳参数和权重。目前,GPU(Graphic Processing Unit,图形处理单元)卡由于其出色的并行矩阵乘法能力和支持的软件,是DL的最佳硬件解决方案。然而,它们的灵活性(游戏支持)使它们对于DL的效率较低,这就是其他DL加速器 ASIC(Application Specific Integrated Circuit,专用集成电路)的用武之地,可提供更好的效率和性能。但是GPU和ASIC都是建立在传统的冯·诺依曼(Von-Neumann,简称vN)架构上的。在内存和处理器之间传输数据所花费的时间和精力(所谓的冯·诺依曼瓶颈)已经成为问题,尤其是对于以数据为中心的应用,例如实时图像识别、自然语言处理,扩展现实XR。为了在vN架构之外实现更大的加速因子和更低的功率,基于非易失性存储器(non-volatile memory,简称NVM)阵列的IMC,如相变存储器(phase change memory,简称PCM)和电阻随机访问存储器(resistive random access memory,简称RRAM)已经被探索。IMC 的向量矩阵乘法取代了 CPU/GPU(数字电路)中昂贵的高功耗矩阵乘法运算,并避免了从/向内存移动权重。因此,它有很大的潜力对DL的性能和功耗产生巨大影响。

3. 用于深度学习的硬件

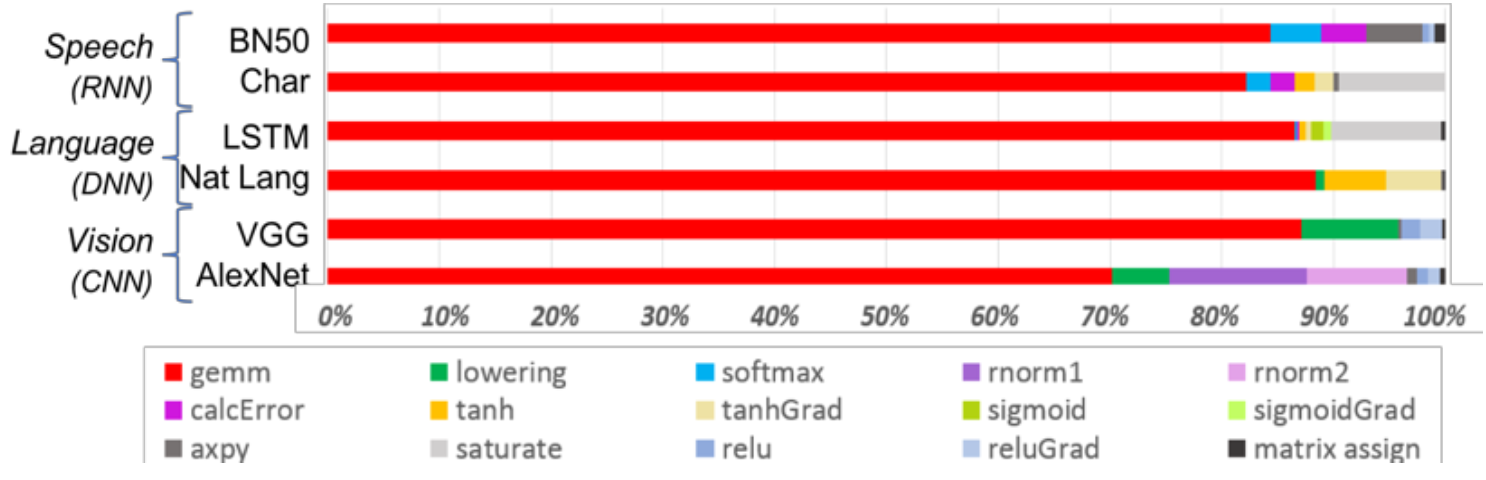

图1 深度学习算法的运算谱

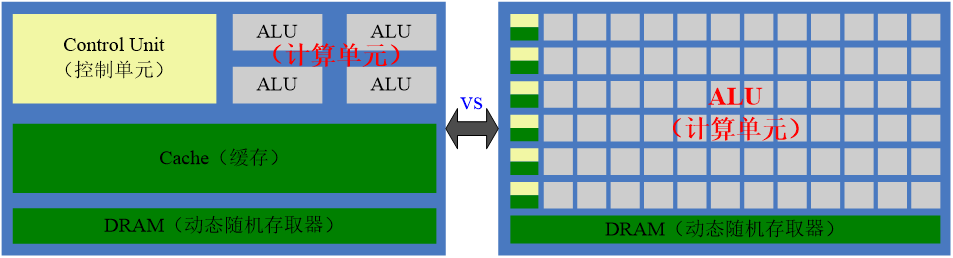

图1[2]显示了DL算法由一系列操作组成(图1中包括6个代表语音、语言和视觉处理的神经网络)。尽管矩阵乘法 (gemm,图1中红色部分) 占主导地位,但在保持精度的同时优化性能效率需要核心架构有效地支持所有辅助功能。图2是CPU和GPU的比较。中央处理器(Central Processing Unit,CPU)是用来处理复杂任务的,如时间切片、复杂控制流和分支、安全性等。相比之下,GPU只能做好一件事。它们处理数十亿个重复的低级任务,比如矩阵乘法。与通常只有4或8个的传统CPU相比,GPU有数千个算术逻辑单元 (Arithmetic Logic Unit,简称ALU)。但是,GPU仍然是一种通用处理器,必须支持数百万种不同的应用程序和软件。对于数千个ALU中的每一个计算,GPU都需要访问寄存器或共享内存来读取和存储中间计算结果。由于 GPU 在其数千个 ALU 上执行更多并行计算,因此它也会按比例花费更多的能量来访问内存,并且还增加了 GPU 用于复杂布线的占用空间。为了解决这些问题,需要用于 DL 的 ASIC,TPU(Tensor Processing Unit,张量处理单元)就是一个例子[3]。

图2 CPU与GPU的架构比较

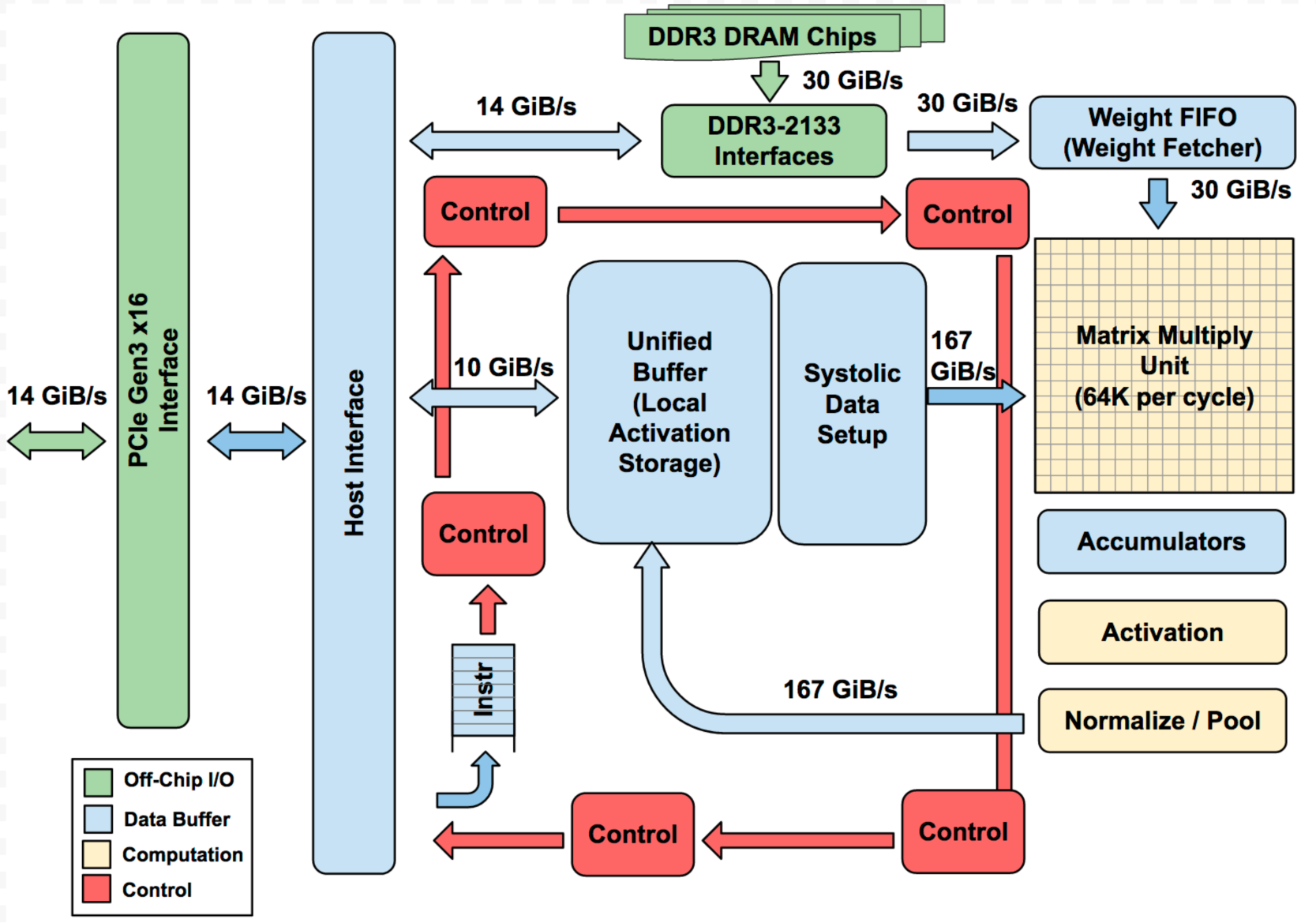

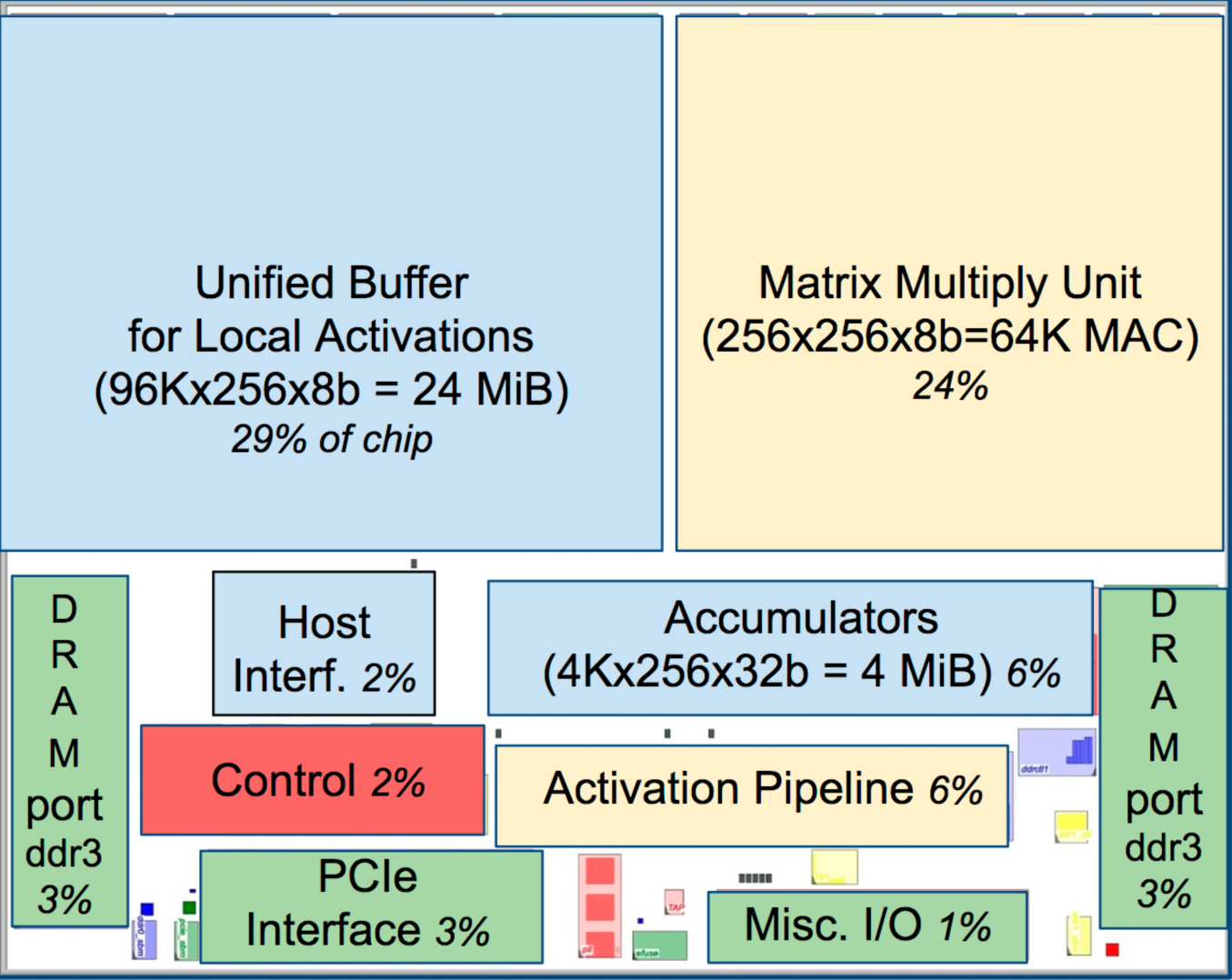

图3(a)(b)分别为TPU芯片的框图和芯片内部平面布局图[3]。它是一种专用于神经网络工作负载的矩阵处理器,能够以极快的速度处理神经网络的大量乘法和加法,同时消耗更少的功率并占用更小的物理空间。其关键推动因素是大幅减少vN瓶颈(从内存中移动数据)。通过了解DNN的目标,TPU放置数千个乘数和加法器,并将它们直接连接起来,形成一个由这些运算符组成的大型物理矩阵。对于操作,首先,TPU 将内存中的权重加载到乘法器和加法器的矩阵中。然后,TPU从内存中加载数据(特性)。随着每次乘法的执行,结果将在求和的同时传递给下一个乘法器。因此输出将是数据和参数之间所有乘法结果的总和。在海量计算和数据传递的整个过程中,根本不需要内存访问。TPU的缺点是失去了灵活性; 它只支持少数特定的神经网络。

(a)框图 (b)内部平面布局图

图3 TPU芯片的框图和内部平面布局图。(a)主要的计算是黄色的Matrix Multiply unit(矩阵乘法单元)。它的输入是蓝色的Weight Fetcher(采用FIFO机制,即权重先进先出,一种数据流机制)和蓝色的Unified Buffer(统一缓冲区),它的输出是蓝色的Accumulators(累加器)。黄色的Activation Unit(激活单元)在Accumulators上执行非线性函数,进入Unified Buffer。(b)浅(蓝色)数据路径是67%,中等(绿色)I/O是10%,而深(红色)的Control(控制)只占2%的面积。在CPU或GPU中Control要大得多(也更难设计)。

4. 用于深度学习的存内计算

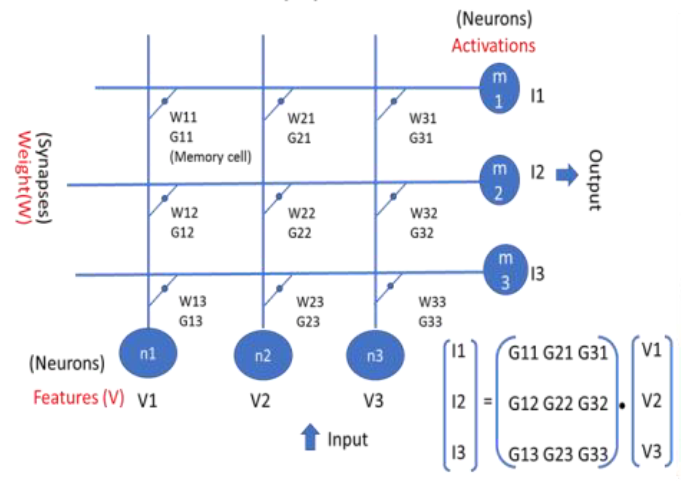

DNN的推理和训练算法主要涉及向量矩阵的正向和反向乘法运算。该操作可以通过存内计算(IMC)在50多年前就已经提出的2D交叉棒存储器阵列上执行[4]。如图4所示,DNN的权重(G)存储在1T(晶体管)-1R(电阻)或1T的存储单元中。通过同时在行上施加电压输入V并从列中读取电流输出I,模拟权重(G)求和是通过基尔霍夫电流定律和欧姆定律实现的。在理想的交叉棒存储阵列中,输入-输出关系可以表示为:I= V·G。矢量-矩阵相乘是通过将输入矢量映射到输入电压V,矩阵映射到电导G,输出映射到电流I来实现的。IMC向量矩阵乘法取代了GPU/TPU(数字电路)中昂贵的高功耗矩阵乘法运算,避免了从内存中移动权重,从而大大提高了DNN的性能和功耗。使用反向传播算法加速DNN训练的演示报道了从27倍[5]到2140倍[6]的加速因子(相对于CPU),并显著降低了功耗和面积。

图4 向量矩阵乘法运算在2D交叉棒存储器阵列上的实现示意图

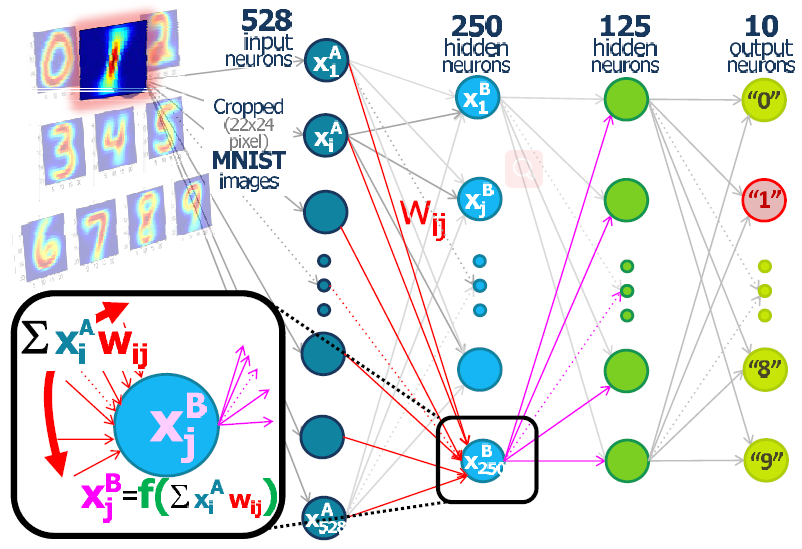

图 5[7]展示了使用PCM器件作为突触(权重)的DNN推理示意图,每一层的神经元通过权重wij和非线性函数f()驱动下一层。输入神经元由来自连续MNIST(机器学习领域中非常经典的一个测试数据集)图像的像素驱动,10个输出神经元识别出现了哪个数字。IMC DNN加速的一个限制是存储器件的缺陷。通常被认为有利于存储应用的器件特性,例如高开/关比、数字按位存储或不相关的特性(如不对称Set和Reset操作)正成为加速DNN训练的限制。完美 IMC DNN存储单元加上对完美电阻器件提出特定要求的系统和CMOS电路设计,可以实现超30000倍(相对于CPU)的加速因子[8]。开发或研究DNN的IMC有很大的收益,但目前市场上还没有产品。阻止它发生的挑战包括:1、存储单元的缺陷(循环耐久性、小动态范围、电阻漂移、非对称编程)。2、层间数据传输(AD、DA转换、数字功能连接)。3、灵活的软件、框架支持(软件可重构IMC DNN)。

图5 采用PCM器件作为突触(权重)的DNN推理实现手写数字识别的示意图

5. 总结

在先进算法和计算硬件(GPU)的帮助下,深度学习将人工智能推向了一个新的水平。数以千计的并行处理ALU使GPU成为强大的机器,可以为DNN操作执行矩阵乘法。通过牺牲灵活性,像TPU一样的ASIC构建的DNN加速芯片可以实现更高的性能和更低的功耗。但利用数字电路进行矩阵乘法有其局限性。为了实现更高的加速因子和更低的功耗,面向DNN的向量矩阵乘法的存内计算IMC方法被提出。IMC虽然为DNN带来了巨大的利益,但也面临着许多挑战。例如:在IMC DNN成为现实之前,需要克服存储单元的缺陷、层间的数据传输以及支持的软件和框架。

参考目录:

[1] Yann LeCun, Yoshua Bengio & Geoffrey Hinton, “Deep learning”, NATURE, Vol. 512, 436-444, (2015).

[2] B. Fleischer et al., “A Scalable Multi-Tera OPS Deep Learning Processor Core for AI Training and Inference”, Symposium on VLSI Circuits, C4-2, (2018).

[3] Norman P. Jouppi et al., “In-Datacenter Performance Analysis of a Tensor Processing Unit”, Proc. of the 44th Annual International Symposium on Computer Architecture, 1-12 (2017).

[4] Kybernetik Steinbuch, “Dielernmatrix”, Kybernetik 1, 36–45 (1961).

[5] G.W.Burr et al., “Large-scale neural networks implemented with non-volatile memory as the synaptic weight element: comparative performance analysis (accuracy, speed, and power)”, Proc. IEDM 15, 76-79 (2015).

[6] J. Seo et al., "On-chip sparse learning acceleration with CMOS and resistive synaptic devices", IEEE Transactions on Nanotechnology (TNANO), Vol. 14, No. 6, 969-979 (2015).

[7] G.W.Burr et al., “Experimental demonstration and tolerancing of a large-scale neural network (165,000 synapses), using phase-change memory as the synaptic weight element”, Proc. IEDM 14, 697-700 (2014).

[8] Tayfun Gokmen & Yurii Vlasov, “Acceleration of deep neural network training with resistive cross-point devices”, Front. Neurosci, Volum 10, article 333, (2016).