基于新兴非易失性存储器件的脑启发计算(三)-张鑫博士

2021-10-14

1. 为什么eNVMs对神经计算的硬件实现有吸引力?

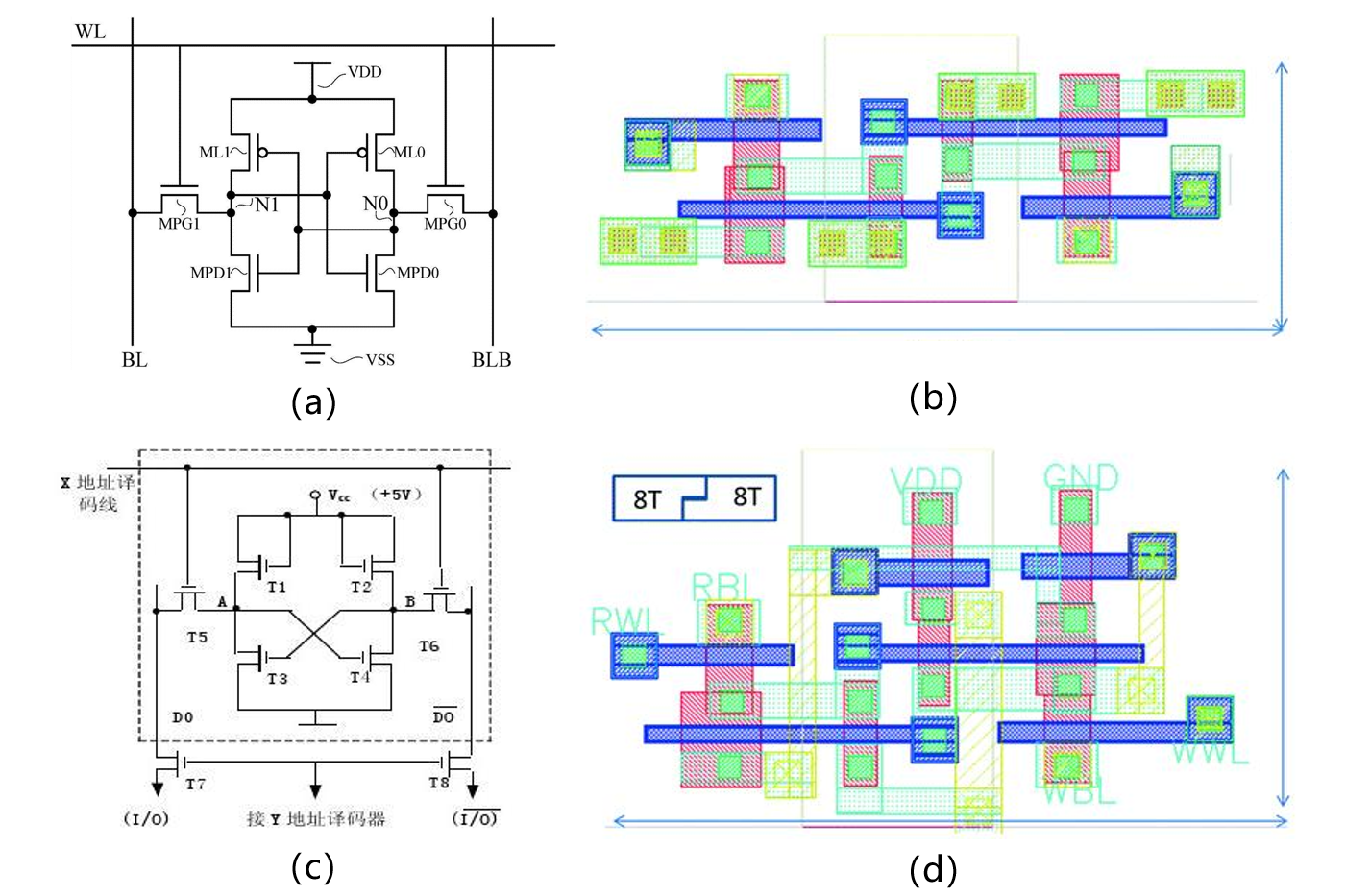

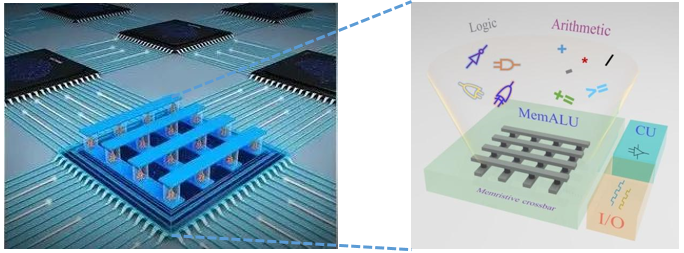

为克服基于静态随机存取存储器SRAM(static random-access memory,被称为volatile memory)的突触所面临的挑战,研究人员提出利用eNVMs(emerging nonvolatile memory)的独特特性更好地服务于神经网络中的模拟突触。目标是用电阻式交叉杆阵列代替SRAM阵列,以更并行的方式存储和/或更新权重。与拥有6个或8个晶体管的二进制SRAM单元相比(如图1所示,面积大,存储信息有限),eNVM单元占用的面积要小几十倍以上,并且每个单元可以存储多个比特,这进一步增加了集成密度,从而支持更大的片上容量(对于更大的问题或数据集)。从整个系统的角度来看,将大部分或所有权重存储在片上,从而减少或消除片外内存访问对加速和降低能耗至关重要。由于非挥发性,eNVM设备也可以立即关闭和打开,没有待机泄漏。此外,与传统的SRAM阵列顺序写和读不同,具有eNVMs的电阻交叉杆阵列可以进行并行编程及加权求和,以进一步加速,有可能实现在线训练。

图1 SRAM电路原理图及版图,(a)6管SRAM原理图;(b)6管SRAM版图;(c)8管SRAM原理图(d)8管SRAM版图。

一般地,eNVMs大多是电阻式存储器,使用电阻来表示和存储数据,而铁电存储器则使用电容来表示和存储数据。基于电阻的eNVMs包括自旋转矩磁随机存取存储器(STT-MRAM)[1]、相变存储器(PCM)[2]和电阻性随机存取存储器(RRAM)[3]。RRAM有两个子类[4]:一个是阴离子型氧化物随机存取存储器(OxRAM),另一个是阳离子型导电桥接随机存取存储器(CBRAM)[5]。在一些文献中,电阻存储器也称为记忆电阻器(忆阻器,memristor)[6]。本文,我们将集中讨论PCM和RRAM技术,因为它们已经被证明具有多级状态,此外还将简要讨论铁电场效应晶体管(FeFET)和浮栅晶体管(目前闪存技术的基本单元)在突触器件中的应用。eNVMs主要是作为具有积极工业研究和开发的下一代存储级存储技术而被研究的[7]。例如,三星已经报告了一款20nm节点8Gb PCM原型芯片,具有40Mb /s的写带宽[8]。闪迪/东芝已经发布了一款24nm节点的32gb RRAM原型芯片[9]。美光/索尼报道了一款27nm节点16Gb的CBRAM原型芯片,具有200Mb/s的写带宽和1Gb/s的读带宽。松下的微控制器商用产品有兆字节容量的嵌入式TaOx RRAM[10]。这些例子表明,eNVMs是潜在的大规模神经网络集成的可行技术。

图2 基于eNVM器件的交叉杆阵列概念示意图

2. 突触器件的器件级特性

2.1 期望特性

电阻性突触器件在提高学习精度和能量效率方面的理想特性在这里将被讨论。表1总结了电阻性突触器件的理想性能指标。值得注意的是,许多指标高度应用依赖的(与不同的场景相关,例如,在线或离线培训,数据集大小等)。

表1 突触器件期望的性能指标

(1)器件尺寸

神经网络的大规模集成需要紧凑的、面积小的突触器件。具有亚10nm扩展特性的电阻性突触器件是首选。当今的RRAM和PCM器件已经证明了这种可伸缩性,但是到目前为止的大多数例子都是针对数字内存应用的。因此,可扩展性和模拟突触特性(如多级状态和动态范围)之间的权衡需要进一步表征。最终,一种与交叉杆阵列结构和三维集成兼容的双端eNVM器件(理想情况下带有双端选择器)是未来研究的目标。

(2)多级状态

在生物突触上观察到的突触可塑性特征表现为具有多级突触权重状态的类似行为。大多数受神经启发的算法也使用模拟突触权值来学习模式或提取特征。一般来说,更多的多级状态(例如,>数百级)可以转化为更好的学习能力和更优的网络鲁棒性。然而,权重精度要求(即电导状态的数量)仍然强烈依赖于应用场景。一般地,在线训练需要比推理更多的状态级别。如果阻性突触器件中的多级状态不足以满足算法精度要求,则有两种替代解决方案:首先,可以将多个器件分组以表示更高的精度,但代价是面积和能耗[11]。其次,最近的工作表明,具有随机权重更新的二元突触设备可以等效地为一些简单的神经网络提供模拟突触的特性[12]。

(3)动态范围

动态范围是最大电导和最小电导之间的开/关比。大多数候选电阻性突触器件表现出2倍至大于100倍的范围。动态范围越大,算法中的权重到器件中的电导的映射能力越好,因为算法中的权重通常在一个范围内(例如,在 0 和 1 之间)进行归一化。例如,开/关比为100意味着可以表示的最小权重为 0.01。考虑到并行读取的功耗,大规模集成神经网络(例如,矩阵大小为512 × 512或以上)中的权重,单个器件所需范围的指导原则可以从10nS 到1μS以便将最大列电流限制在数百μA以便于进行实际电路设计。

参考目录:

[1] J.-G. Zhu, “Magnetoresistive random access memory: The path to competitiveness and scalability,” Proc. IEEE, vol. 96, no. 11, pp. 1786–1798, Nov. 2008.

[2] H.-S. P. Wong et al., “Phase change memory,” Proc. IEEE, vol. 98, no. 12, pp. 2201–2227, Dec. 2010.

[3] H.-S. P. Wong et al., “Metal-oxide RRAM,” Proc. IEEE, vol. 100, no. 6, pp. 1951–1970, Jun. 2012.

[4] A. Graves, A.-R. Mohamed, and G. Hinton, “Speech recognition with deep recurrent neural networks,” in Proc. IEEE Int. Conf. Acoust. Speech Signal Process. (ICASSP), May 2013, pp. 6645–6649.

[5] ImageNet. [Online]. Available: http://www. image-net.org/

[6] J. J. Yang, D. B. Strukov, and D. R. Stewart, “Memristive devices for computing,” Nature Nanotechnol., vol. 8, no. 1, pp. 13–24, 2013.

[7] S. Yu and P. Y. Chen, “Emerging memory technologies: Recent trends and prospects,” IEEE Solid-State Circuits Mag., vol. 8, no. 2, pp. 43–56, 2016.

[8] Y. Choi et al., “A 20 nm 1.8 V 8Gb PRAM with 40 MB/s program bandwidth,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2012, pp. 46–48.

[9] T.-Y. Liu et al., “A 130.7 mm 2 2 -layer 32 Gb ReRAM memory device in 24nm technology,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, 2013, pp. 31.6.1–31.6.4.

[10] cross-point ReRAM macro with 443MB/s write throughput,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, 2012.

[11] S. Yu, “Binary neural network with 16 Mb RRAM macro chip for classification and online training,” in IEDM Tech. Dig., Dec. 2016.

[12] S. Yu, B. Gao, Z. Fang, H. Yu, J. Kang, and H.-S. P. Wong, “Stochastic learning in oxide binary synaptic device for neuromorphic computing,” Front. Neurosci., vol. 7, p. 186, Oct. 2013.