基于新兴非易失性存储器件的脑启发计算-张鑫博士

2021-07-07

基于新兴非易失性存储器件的脑启发计算(一)

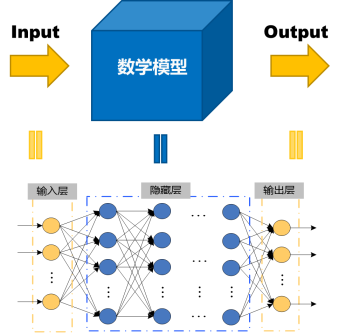

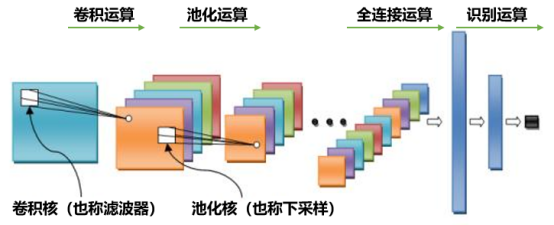

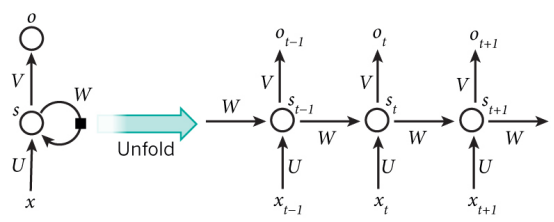

能够让机器像人类一样思考和行动的人工智能(Articicial Intelligence,AI)正在复兴,它不仅是当今学术界的热门话题,而且具有显著的社会影响(例如,AlphaGo的出现[1])。近年来,人工神经网络(即机器/深度学习)在大规模的视觉/听觉识别和分类任务中显示出了显著提高的准确率,有的准确率甚至超过了人类的水平[2]。图1为一种基本的深度神经网络示意图,包含输入层,隐藏层和输出层。特别是卷积神经网络(Convolutional Neural Network,CNN)[3]和循环神经网络(Recurrent NN,RNN)[4]算法及其变体已经证明了它们在图像、视频、语音和生物医学应用中的有效性。图2和图3分别给出了CNN和RNN的示意图。为了提高精度,目前最先进的深度学习算法倾向于积极地增加神经网络的深度和规模。例如,微软的Res-Net(它赢得了ImageNet 2015图像分类比赛[5])的深度超过了100层[6]。这对硬件实现在计算、内存和通信资源方面提出了重大挑战。例如,谷歌的堆叠自动编码算法能够成功地从YouTube视频中拍摄的1000万张随机图像中识别猫的面孔[7]。然而,这项任务是在一个由16000个处理器核组成的集群上完成的,该集群消耗大约100千瓦的电力,并且需要3天时间来训练网络。

图1 深度神经网络运算示意图

图2 卷积神经网络运算示意图

图3 循环神经网络结构图(左)及其展开形式(右)

如今,深度学习通常是通过数据中心或云平台上的图形处理单元(Graphic Processing Unit,GPU)加速器进行训练的。专门设计的加速器,如Manchester的SpiNNaker[8](图4),Heidelberger的BrainScaleS[9] (图5)和谷歌的张量处理单元(Tensor Processing Unit,TPU[10]已经被开发出来运行大规模的神经形态学和/或深度学习算法。在嵌入式系统或物联网(Internet of Things,IoT)边缘计算方面,如自动驾驶、智能传感器、可穿戴设备等,在性能、功率、面积等方面存在着严重的设计约束。在硅互补金属氧化物半导体(CMOS)技术中,IBM的TrueNorth[11]、MITs Eyeriss[12]和一系列CNN加速器[13]-[15]已经开发出了专用集成电路(ASIC)片上解决方案。然而,在片内内存容量、片外内存访问和在线学习能力方面仍然存在局限性。特别是CMOS ASIC设计表明,片上存储是能效计算的最大瓶颈,即存储数百万参数并将它们从片外主存加载到片上缓存需要大量的能量和延迟。今天的CMOS ASIC加速器通常利用静态随机存取存储器(SRAM)作为芯片上的突触存储器。虽然SRAM技术已经很好地跟上了CMOS的缩放趋势,但SRAM的密度(每比特单元100~200F2;其中F表示技术节点)和片上SRAM容量(通常为几兆字节)不足以存储深度学习算法中的大量参数(通常为几百兆字节)。传统SRAM阵列的逐行操作限制了系统的并行性,并且泄漏电流是不可取的。

作为一种可替代的硬件平台,新兴的非易失性存储器件(emerging Nonvolatile Memory,eNVM)被提出用于具有更高密度(通常为每比特单元4~12F2)的片上权值存储和具有低泄漏功耗[16]的快速并行模拟计算。一个能显示多级电阻/电导状态的eNVM器件的特殊子集可以自然地模拟神经网络中的突触器件,即电阻突触器件[17]。电阻性突触器件的例子包括双端eNVMs,如相变存储器(Phase Change Memory,PCM),阻变随机存取存储器(Resistive Random Access Memory,RRAM),以及三端铁电晶体管和浮栅存储器(具有模拟阈值电压)。电阻交叉杆阵列矩阵向量乘法(或点积)的并行性进一步显著加速了核心神经计算(即加权求和)。IBM最近的一项分析显示,与传统GPU相比[18],基于PCM的加速器能够以更低的功耗训练全连接的多层感知器(Multilayer Perceptron,MLP)。通过优化器件技术参数,基于eNVM的加速器有可能优于基于CMOS-ASIC的SRAM突触阵列的加速器[19]。

在过去的几年中,基于eNVM的突触器件和集成到阵列级的研究取得了显著的进展。在器件级,许多具有数十至数百级电导状态的电阻突触器件候选已被证明。电阻式突触器件可以模拟生物突触,在固体介质(例如氧化物/硫族化合物)中离子或原子的迁移/重排可以调节两个电极之间的电导,类似于生物突触通过电压门控钙离子通道的激活来调节其电导。在阵列级,已经有一些使用软件和/或芯片外控制器的小规模(如12 × 12)到中等规模(如256 × 256)的简单神经网络算法的实验演示。这些演示展示了芯片上CMOS控制器的未来大规模集成和原型的巨大前景。此外,当阵列尺寸扩大时,计算机辅助设计(Computer-aided Design,CAD)或电子设计自动化(Electronic Design Automation,EDA)工具的开发促进了器件性能与电路/架构和算法的共同优化,以解决与器件产量、器件可变性和阵列寄生有关的设计挑战。开拓性的仿真框架已经开发出来评估器件级非理想性(有限的权值精度、权值更新非线性/非对称性、变化/噪声等 )对学习精度和训练速度/能量之间的权衡的影响。

参考目录:

[1]D. Silver et al., “Mastering the game of go with deep neural networks and tree search,” Nature, vol. 529, pp. 484–489, 2016.

[2]Y. LeCun, Y. Bengio, and G. Hinton, “Deep learning,” Nature, vol. 521, pp. 436–444, May 2015.

[3]A. Krizhevsky, I. Sutskever, and G. E. Hinton, “ImageNet classification with deep convolutional neural networks,” in Proc. Adv. Neural Inf. Process. Syst. (NIPS), 2012, pp. 1097–1105.

[4]A. Graves, A.-R. Mohamed, and G. Hinton, “Speech recognition with deep recurrent neural networks,” in Proc. IEEE Int. Conf. Acoust. Speech Signal Process. (ICASSP), May 2013, pp. 6645–6649.

[5]ImageNet. [Online]. Available: http://www. image-net.org/

[6]K. He, X. Zhang, S. Ren, and J. Sun, “Deep residual learning for image recognition,” in Proc. IEEE Conf. Comput. Vis. Pattern Recognit. (CVPR), Jun. 2016, pp. 770–778.

[7]Q. V. Le, “Building high-level features using large scale unsupervised learning,” in Proc. Int. Conf. Mach. Learn. (ICML), 2012, pp. 8595–8598.

[8]S. B. Furber, F. Galluppi, S. Temple, and L. A. Plana, “The SpiNNaker project,” Proc. IEEE, vol. 102, no. 5, pp. 652–665, May 2014.

[9]S. Schmitt et al., “Neuromorphic hardware in the loop: Training a deep spiking network on the BrainScaleS wafer-scale,” in Proc. Int. Joint Conf. Neural Netw. (IJCNN), 2017.

[10]N. P. Jouppi et al., “In-datacenter performance analysis of a tensor processing unit,” in Proc. ACM/IEEE Int. Symp. Comput. Architecture (ISCA), 2017.

[11]P. A. Merolla, “A million spiking-neuron integrated circuit with a scalable communication network and interface,” Science, vol. 345, no. 6197, pp. 668–673, Aug. 2014.

[12]Y.-H. Chen, T. Krishna, J. Emer, and V. Sze, “Eyeriss: An energy-efficient reconfigurable accelerator for deep convolutional neural networks,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2016, pp. 262–263.

[13]J. Sim, J.-S. Park, M. Kim, D. Bae, Y. Choi, and L.-S. Kim, “A 1.42 TOPS/W deep convolutional neural network recognition processor for intelligent IoE systems,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Jan. 2016, pp. 264–265.

[14]G. Desoli, “A 2.9 TOPS/W deep convolutional neural network SoC in FD-SOI 28nm for intelligent embedded systems,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 238–239.

[15]B. Moons, R. Uytterhoeven, W. Dehaene, and M. Verhelst, “ENVISION: A 0.26-to-10TOPS/W subword-parallel dynamic-voltage-accuracy-frequencyscalable convolutional neural network processor in 28 nm FDSOI,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 246–247.

[16]S. Yu, Ed., Neuro-Inspired Computing Using Resistive Synaptic Devices. New York, NY, USA: Springer-Verlag, 2017.

[17]D. Kuzum, S. Yu, and H.-S. P. Wong, “Synaptic electronics: Materials, devices and applications,” Nanotechnology, vol. 24, no. 38, p. 382001, 2013.

[18]G. W. Burr et al., “Large-scale neural networks implemented with non-volatile memory as the synaptic weight element: Comparative performance analysis (accuracy, speed, and power),” in IEDM Tech. Dig., 2015.

[19]B. Rajendran et al., “Specifications of nanoscale devices and circuits for neuromorphic computational systems,” IEEE Trans. Electron Devices, vol. 60, no. 1, pp. 246–253, Jan. 2013.