边缘设备神经网络硬件架构发展-张鑫博士

2021-04-16

1. 基于传统计算架构的深度神经网络

基于深度神经网络(Deep Neural Network,DNN)的机器学习(Machine Learning,ML)算法在图像/语音识别、自动驾驶等人工智能(Artificial Intelligence,AI)应用领域取得了巨大的成就。然而,这些基于DNN的算法在基于冯诺依曼(Von-Neumann)架构的传统计算平台(如中央处理器CPU、图形处理器GPU)上的计算成本很高,因为涉及到密集的向量-矩阵乘法(Vector-Matrix Multiplications,VMM)。基于CPU的计算平台由于计算并行性不足,无法充分利用DNNs所涉及的数据或模型级并行性。此外,先进的DNNs具有数百万个权重参数,这需要在计算过程中在CPU和主存储器之间进行密集的数据移动。由于总线带宽不足(即所谓的“内存墙”瓶颈),这样的数据移动在延迟和能量消耗方面是昂贵的。基于GPU的计算平台由于具有高的多核计算并行性,为DNN处理提供了高吞吐量,这使得它在DNN训练(Training)中非常受欢迎。然而,在功率和面积预算有限的情况下,高能耗使其无法部署到DNN现场训练和后续推理(Inference)的边缘设备上[1]。

2. 基于ASIC设计的DNN

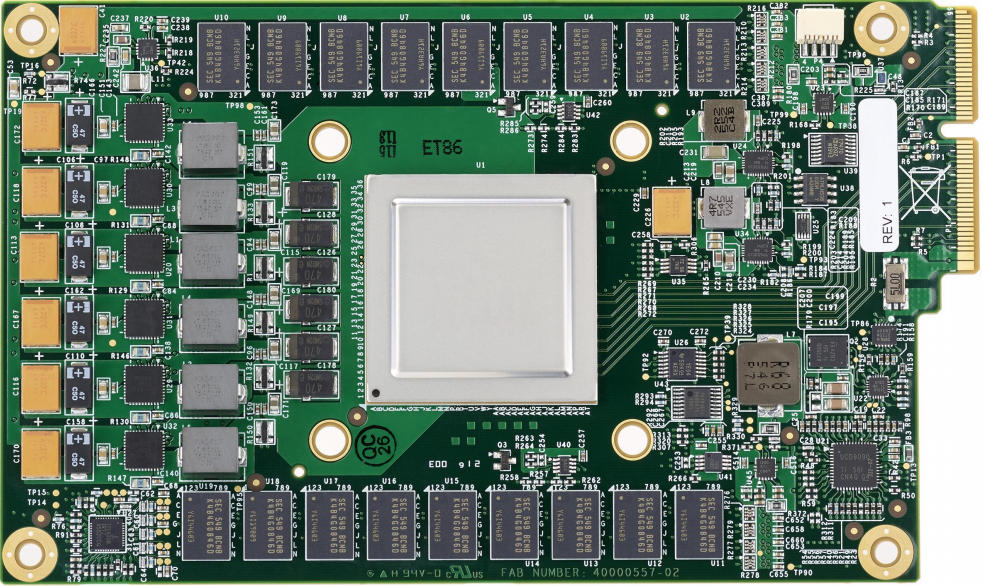

专用集成电路(Application Specific Integrated Circuit,ASIC)设计被提出以加速DNN训练和推理[2,3],一个基于ASIC方式设计的专用芯片张量处理单元(Tensor Processing Unit,TPU)及其印刷电路板如图2所示。这些设计通过利用DNN处理过程中的数据和模型级并行性来实现良好的吞吐量。此外,通过最大限度地重用数据,降低了处理单元(Processing Elements,PE)与主内存之间数据移动的能量和延迟。例如,Eyeriss提出了行平稳(Row Stationary,RS)数据流,最大限度地重用过滤器权重和输入特征映射(Input Feature Maps,IFM),以减少数据移动的能量消耗[3]。

图2 TPU印刷电路板[2]

3. 基于CIM架构的DNN

为了进一步降低数据移动的能量消耗、提高吞吐量,一种在内存阵列内进行VMM来加速DNN的架构被提出,称为存内计算(Compute-in-memory,CIM)范式[4]。

3.1 基于SRAM的CIM

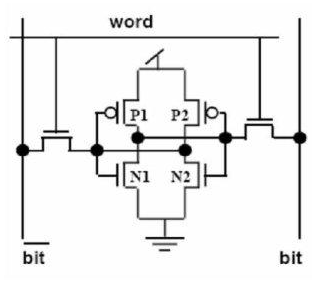

作为一种成熟的CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)技术,基于SRAM(静态随机存取存储器,Static Random Access Memory)的CIM方案被提出[5,6]。然而,由于SRAM的易失性,在开始推理前,权重需要从非易失性存储器(Non-Volatile Meomory,NVM)(如闪存)加载,这增加了能量消耗,阻碍了实时响应。另一方面,保持供电会导致显著的SRAM泄漏功率,从而进一步降低其能效。

图3 典型的6管SRAM单元

3.2 基于eNVMs的CIM

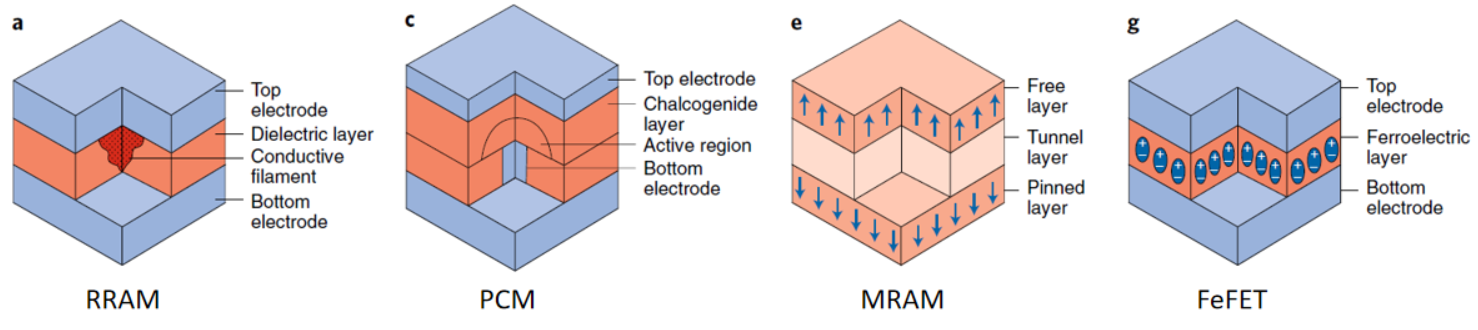

随着新兴非易失性存储器(emerging NVM,eNVM)技术的发展[7],基于eNVMs的CIM成为DNN加速的理想选择[8-11]。这些eNVM技术包括自旋-传递-转矩磁性随机存储器(STT-MRAM)[12]、阻变随机存储器(RRAM)[13]、相变存储器(PCM)[14]和铁电场效应晶体管(FeFET)[15],相比于传统基于CMOS的SRAM技术(如果在相同的制程上),它们在非易失性、低泄漏和高集成度方面表现出优势。

图4 四种eNVM设备简略图[16]

然而,尽管已经证明CIM方案对于在DNN推理方面具有时间和能源效率,但基于CIM的DNN原位训练仍然存在挑战,原因如下:1)由于eNVM设备的非线性和非对称权重更新行为,训练精度显著下降[14];2)与SRAM技术相比,eNVMs具有较高的写延迟和写能耗;3)由于存储单元在训练过程中频繁编程,eNVMs的写入容限有限,导致写入失败。

4. 基于混合精度突触的CIM

随着个性化需求的不断增长,网络模型也出现了边缘个性化的新趋势,这就使得边缘现场训练成为必要。训练个性化的神经网络需要个人数据,这在GPU/云训练期间是无法使用的。但是,出于隐私考虑,用户不愿将个人数据发送到云端。因此,一种方法是先在云上训练一个支持通用任务的网络模型,然后将用户数据在边缘设备上训练,使其个性化。

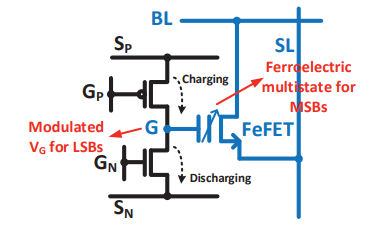

图5 电路模拟的混合精度突触单元[15]

为了使得边缘设备上的原位训练可靠和有效,最近,一种混合精度突触被提出(图5)[15],其中,eNVMs和电容器被组合起来,利用eNVMs的非易失性和大动态范围,以及电容器具有的对称、快速和能效高的充/放电行为特性。在训练阶段,梯度在电容器上积累。经过一定数量的训练批次后,将存储在电容器中的权值读出并转移到eNVMs中,以避免由于电容器保留时间有限而导致数据丢失。训练后,只有存储在eNVMs中的权重被用于推理,与纯SRAM方法和在单独芯片上进行训练和推理的方法相比,这消除了权重负荷,并提高了能效。

据报道,在简单MNIST数据集上,采用混合精度突触的多层感知机(Multi-Layer Perceptron,MLP)网络具有与软件原位训练可比拟的精度和前景良好的能效[17,18]。然而,使用混合精度突触的架构级设计还没有得到证实。不同的eNVM技术对系统级性能的影响尚未得到彻底的研究。此外,该设计是否适用于大规模的DNN训练,在处理时间显著增加的情况下,电容的数据保留量有限,值得怀疑。