基于非易失存储器动态权衡特性的体系结构-姚卫博士

2021-04-16

目前,制约新型非易失存储器(NVM)广泛应用的主要问题包括写延迟长、写操作动态功耗高、写寿命有限[1]。针对这些问题,传统的解决方法是利用计算机体系结构的方法,通过增加层或者调度的方式加以避免或隐藏。但是,这类解决方案往往存在软硬件开销大、无法同时针对不同问题进行优化等问题。近年来,随着对新型非易失存储材料研究的深入,一系列器件自身所包含的动态权衡特性被陆续发现,这也为体系结构研究提供了新的机遇。基于这些器件自身的动态权衡特性,研究人员提出了一系列新的动态非易失存储器优化方案。与传统的优化方案相比,这类新型方案具有额外硬件开销小、可同时针对多个目标进行优化等优点。

随着对NVM存储材料的深入研究,人们发现在NVM存储材料中存在一些相互影响的参数,在其工作状态下,可以通过改变一个参数,使其他相关参数向着相反方向变化,这种特性被称为“动态权衡特性”[2-4]。NVM存储材料中存在的动态权衡特性包括存储密度与写延迟的关系、写延迟与写寿命的关系、写延迟与状态保持时间的关系。

1. 存储密度与访问延迟的关系

对于使用电阻值表示逻辑值的NVM材料(如ReRAM, PCM),可通过对其不同电阻值进行重新编码,实现在单一存储单元中存储多个逻辑状态。该技术被称为多层(MLC)NVM,可用于提高存储密度或存储可靠性。对于MLC NVM而言,由于需要精确控制写入后存储单元的电阻值,因此MLC NVM的写操作通常采用基于多次迭代的模型。

优化方法:通过适当牺牲存储密度换取系统性能;在部分特定应用中,存储空间不足会带来明显的性能损失,因此在这些应用中可以通过适当增加写访问延迟而动态提升存储密度。这样虽然增大了写访存操作的延迟,但存储容量的提升依然可以使系统整体性能得到提升。主要优化方法有弹性存储,动态可伸缩目录表,基于弹性存储的Hash Table算法优化。

2. 写延迟与写寿命的关系

在多种NVM材料中,写延迟都与器件寿命存在相关关系。为了缩短写操作的延迟,往往需要在执行写操作时使用更多的能量,而过高的能量将加速器件的老化,进而导致器件寿命的降低。

基于写延迟与写寿命的关系优化方法:文献[5]提出了一种名为Mellow Write的技术,在尽量减少额外硬件开销的前提下提升NVM存储器的寿命。与原有基于写分摊和减少写操作的思路不同,Mellow Write主要通过延长写操作延迟(“慢写”)减少单次写操作对NVM存储单元的磨损程度,从而实现延长存储器寿命的目标。

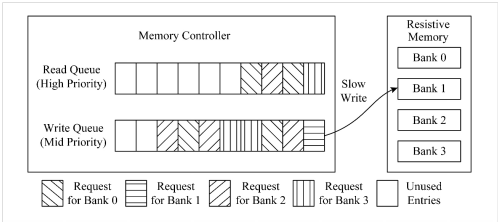

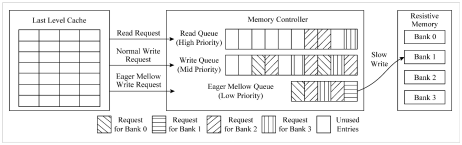

为了减少写延迟延长对系统性能的影响,Mellow Write包含了2种策略:Bank-Aware Mellow Write和Eager Mellow Write。如图1所示,在Bank-Aware Mellow Write策略中,通过扫描写访存队列中的写请求,当一个bank只有一个写请求时,该请求会采用慢写的方式完成。为了进一步提升Mellow Write的性能,在Eager Mellow Write策略中(如图2所示),通过对末级缓存(last level cache, LLC)进行扫描,挑选无用的“脏数据”并将其主动地采用慢写的方式进行写回。同时,在内存控制器中增加了专门的Eager Mellow Write Queue用于主动生成的慢写请求。

图1. Bank-Aware Mellow Write写策略[5]

图2. 采用Eager Mellow Write策略的系统结构图[5]

3. 写延迟与状态保持时间的关系

在MLC PCM 存储器中,由于制造工艺中存在的误差、材料自身成分的波动以及自身结构的细微变化,在擦写时电流、电压和持续时间相同,PCM存储器中不同单元阻值的变化情况也并不严格一致。因此,为了确保擦写的准确性,MLC PCM的写操作通常采用一种基于多次迭代的策略,每次迭代中包含一组“擦写-验证”操作。在每次写操作开始前,通常会使用一个RESET操作使得存储单元恢复到初始状态,随后采用多次“擦写-验证”操作直至存储单元的电阻值达到目标值。

优化方法:基于这一动态权衡关系的体系结构主要有嵌入式系统主存储器,通用计算系统主存储器以及其他存储设备。