基于自治结构的忆阻存储器结构-姚卫博士

2021-04-07

当前,传统的基于CMOS工艺的存储技术已经接近发展极限,集成电路设计已进入“后摩尔”时代。来自IDC的数据,2019年全球的数据量已达到41ZB,但全球数据量一直在高速增长。日益庞大的数据量对存储包括高性能计算的存储的要求会越来越高。所以,必须寻找不同于传统CMOS器件存储机理的新型存储介质,来制造体积更小、容量更大、功耗更低、可靠性更高的存储器[1]。忆阻器具有高读写速度、高集成密度、低功耗、CMOS工艺兼容性等特性[2-3],且具有非易失特性,即存储的信息在掉电情况下不会丢失[4],因此,忆阻器被视为下一代理想的存储器件[5-6]。

基于忆阻器交叉阵列的存储器具有非易失、高密度存储的优点,目前,已有较多类型的数据存储结构。下面根据已有文献[7-10]介绍基于“数据HOME自治结构”的忆阻存储器结构。

首先,介绍“数据HOME自治”的相关概念。数据HOME自治定义:数据可在其存放位置进行不受外界干扰的自我管理,实现预定的操作和服务的数据处理机制[1,7]。采用数据HOME自治原理实现的存储结构称为“数据HOME自治结构” [1,7]。

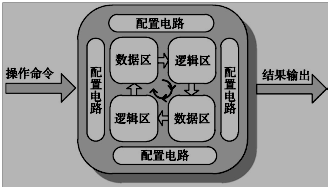

文献[7-9]提出了一种基于忆阻器的“数据HOME自治”结构图,如图1所示。从图1中可以看出,该结构由数据区、逻辑区和配置电路3个部分组成。其中,数据区用于存储数据;逻辑区进行逻辑运算,用于对区域内的数据进行处理;配置电路配合逻辑区完成运算并控制数据区和逻辑区的轮换[7-9]。

图1 基于忆阻器的“数据HOME自治”结构

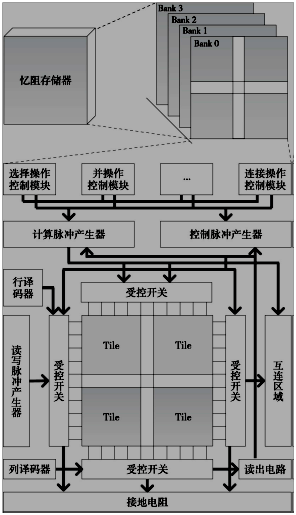

根据“数据HOME自治”原理和基于忆阻器的“数据HOME自治”结构,图2展示了一种忆阻存储器结构[1,7-10]。忆阻存储器可由多个Bank构成,而每个Bank又由多个忆阻Tile和多个功能部件构成。图2中的忆阻存储器由4个忆阻Bank构成,其中Bank 0中包含4个忆阻Tile和多种功能部件。

图2 忆阻存储器结构

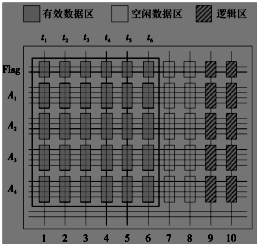

另外,忆阻Tile是指忆阻存储器中用于数据存储和逻辑运算的忆阻器交叉阵列区域,是忆阻存储器中数据的驻地,也是对数据进行状态逻辑操作的基本单位。文献[7]设计了一种忆阻Tile结构图,如图3所示。

图3 忆阻Tile结构[7]

目前,支持状态逻辑计算的存储结构[1, 7-12]主要分为忆阻存储器结构和忆阻Tile结构,这些电路设计通常包括忆阻交叉阵列结构、外围电路与脉冲序列发生器三个部分。文献[1]指出了这类设计的优势是以“数据HOME”结构为理论指导,并设计了功能模块完整的、具有自主运算能力的存储结构;但缺点是没有制作出实际的忆阻存储器。